FlexQ™II

# 3.3 Volt Synchronous x18 First-In/First-Out Queue

| Memory Configuration | Device  |

|----------------------|---------|

| 262,144 x 18         | FQV2105 |

| 131,072 x 18         | FQV295  |

| 65,536 x 18          | FQV285  |

| 32,768 x 18          | FQV275  |

| 16,384 x 18          | FQV265  |

| 8,192 x 18           | FQV255  |

# **Key Features**

- Industry leading First-In/First-Out Queues (up to 133MHz)

- Write cycle time of 7.5ns independent of Read cycle time

- Read cycle time of 7.5ns independent of Write cycle time

- 3.3V power supply

- 5V input tolerant on all control and data input pins

- 5V output tolerant on all flags and data output pins

- Master Reset clears all previously programmed configurations including Write and Read pointers

- Partial Reset clears Write and Read pointers but maintains all previously programmed configurations

- First Word Fall Through (FWFT) and Standard Timing modes

- Presets for eight different Almost Full and Almost Empty offset values

- Parallel/Serial programming of PRAF and PRAE offset values

- Full, Empty, Almost Full, Almost Empty, and Half Full indicators

- Asynchronous output enable tri-state data output drivers

- Data retransmission

- Available package: 64 pin Plastic Thin Quad Flat Pack (TQFP), 64 pin Slim Thin Quad Flat Pack (STQFP)

- (0°C to 70°C) Commercial operating temperature available for cycle time of 7.5ns and above

- (-40°C to 85°C) Industrial operating temperature available for cycle time of 7.5ns and above

# **Product Description**

HBA's FlexQ<sup>™</sup> II offers industry leading FIFO queuing bandwidth (up to 3.0 Gbps), with a wide range of memory configurations (from 8,192 x 18 to 262,144 x 18). System designer has full flexibility of implementing deeper and wider queues using FWFT mode and width expansion features. Full, Empty, and Half-Full indicators allow easy handshaking between transmitters and receivers. User programmable Almost Full and Almost Empty (Parallel/Serial) indicators allow implementation of virtual queue depths.

5V tolerant on all input and output pins allow easy interfacing with devices operating at higher voltage levels. Asynchronous Output Enable pin configures the tri-state data output drivers. Independent Write and Read controls provide rate-matching capability.

Master Reset clears all previously programmed configurations by providing a low pulse on  $\overline{\text{MRST}}$  pin. In addition, Write and Read pointers to the queue are initialized to zero. Partial Reset will not alter previously programmed configurations but will initialize Write and Read pointers to zero.

In FWFT mode, first data written into the queue appears on output data bus after the specified latency period at the low to high transition of RCLK. Subsequent reads from the queue will require asserting  $\overline{\text{REN}}$ . This feature is useful when implementing depth expansion functions. In this mode,  $\overline{\text{DRDY}}$  and  $\overline{\text{QRDY}}$  are used instead of  $\overline{\text{FULL}}$  and  $\overline{\text{EMPTY}}$  respectively.

In Standard mode, always assert  $\overline{\text{REN}}$  for read operation.  $\overline{\text{FULL}}$  and  $\overline{\text{EMPTY}}$  are used instead of  $\overline{\text{DRDY}}$  and  $\overline{\text{QRDY}}$  respectively.

$\overline{PRAF}$ ,  $\overline{PRAE}$ , and  $\overline{HALF}$  are available in either FWFT or Standard mode.

# **Product Description (Continued)**

At any time, data previously read from the queue can be retransmitted by asserting  $\overline{\text{RET}}$  pin at the low to high transition of RCLK for a retransmit operation. Retransmit initializes the Read pointer to zero. Hence, all re-reads will always start from the physical 0<sup>th</sup> (Read pointer = zero) location of the queue. Both zero and normal latency timing modes are available for retransmit operation.

These FlexQ<sup>™</sup> II devices have low power consumption, hence minimizing system power requirements. In addition, industry standard 64 - pin Plastic TQFP and 64 - pin STQFP are offered to save system board space.

These queues are ideal for applications such as data communication, telecommunication, graphics, multiprocessing, test equipment, network switching, etc.

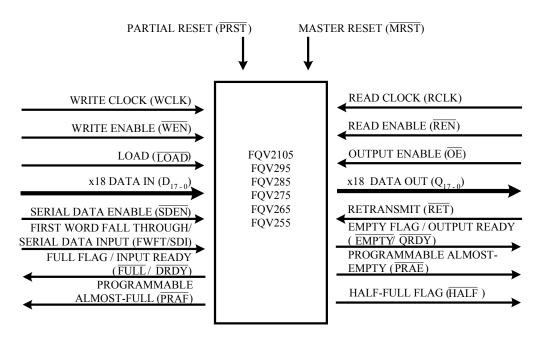

# Block Diagram of Single Synchronous Queue 262,144 x 18 / 131,072 x 18 / 65,536 x 18 / 32,768 x 18 / 16,384 x 18 / 8,192 x 18

#### Figure 1. Single Device Configuration Signal Flow Diagram

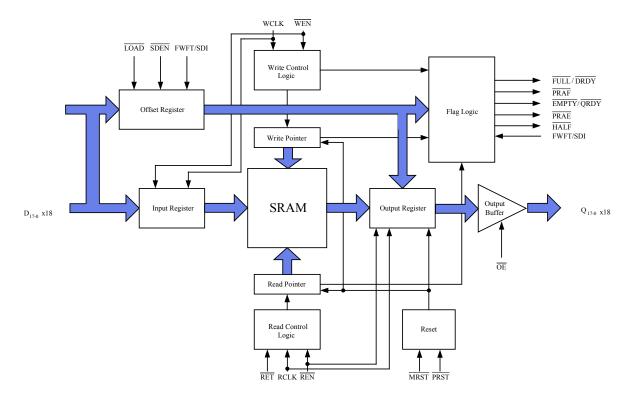

Figure 2. Device Architecture

# NOTES:

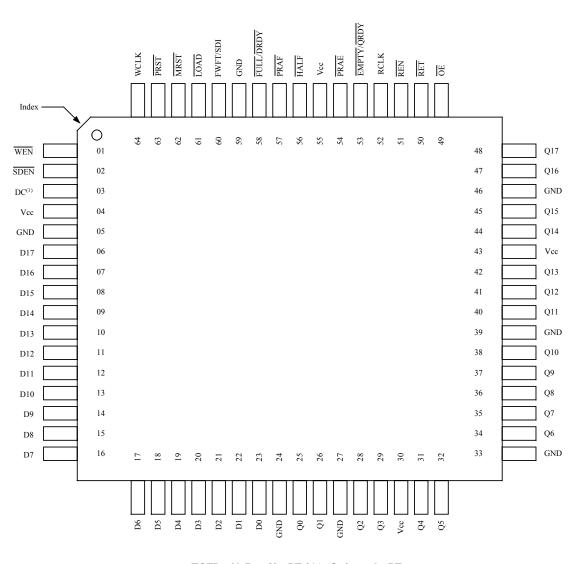

1. DC = Don't Care. Must be tied to GND or Vcc, cannot be left open.

Figure 3. Device Pin Out

3F218C

| Pin #                                                                 | Pin Name                                        | Pin Symbol        | Input/Output | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------------------------------------------------------------|-------------------------------------------------|-------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 62                                                                    | Master Reset                                    | MRST              | Input        | Master Reset is required to initialize Write and Read pointers to the first position of the queue by setting $\overline{\text{MRST}}$ low. In Standard mode, $\overline{\text{FULL}}$ and $\overline{\text{PRAF}}$ will go high; $\overline{\text{EMPTY}}$ and $\overline{\text{PRAE}}$ will go low. In FWFT mode, $\overline{\text{DRDY}}$ will go low and $\overline{\text{QRDY}}$ will go high. $\overline{\text{PRAF}}$ and $\overline{\text{PRAE}}$ will go to the same state as Standard mode. In both modes, all data outputs will go low. Previous programmed configurations will not be maintained |

| 63                                                                    | Partial Reset                                   | PRST              | Input        | Partial Reset is required to initialize Write and Read pointers to the first position of the queue by setting $\overrightarrow{PRST}$ low. In Standard mode, $\overrightarrow{FULL}$ and $\overrightarrow{PRAF}$ will go high; $\overrightarrow{EMPTY}$ and $\overrightarrow{PRAE}$ will go low. In FWFT mode, $\overrightarrow{DRDY}$ will go low and $\overrightarrow{QRDY}$ will go high. $\overrightarrow{PRAF}$ and $\overrightarrow{PRAE}$ will go to the same state as Standard mode. In both modes, all data outputs will go low. Previous programmed configurations will be maintained             |

| 64                                                                    | Write Clock                                     | WCLK              | Input        | Writes data into queue during low to high transitions of WCLK if $\overline{\text{WEN}}$ is set to low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1                                                                     | Write Enable                                    | WEN               | Input        | Controls write operation into queue or offset registers during low to high transition of WCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 61                                                                    | Load Enable                                     | LOAD              | Input        | During Master Reset, set $\overline{\text{LOAD}}$ low to select parallel<br>programming or one of eight default offset values. Set $\overline{\text{LOAD}}$ high<br>to select serial programming or one of eight default offset values.<br>After Master Reset, $\overline{\text{LOAD}}$ controls write/read, to/from offset<br>registers during low to high transition of WCLK/RCLK<br>respectively. Use in conjunction with $\overline{\text{WEN}} / \overline{\text{REN}}$ .                                                                                                                              |

| 6,7,8,9,<br>10,11,12,13,<br>14,15,16,17,<br>18,19,20,21,<br>22,23     | Data Inputs                                     | D <sub>17-0</sub> | Input        | 18 - bit wide input data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 52                                                                    | Read Clock                                      | RCLK              | Input        | Reads data from queue during low to high transitions of RCLK if $\overline{\text{REN}}$ is set to low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 51                                                                    | Read Enable                                     | REN               | Input        | Controls read operation from queue or offset registers during low to high transition of RCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 49                                                                    | Output Enable                                   | ŌĒ                | Input        | Setting $\overline{OE}$ low activates the data output drivers. Setting $\overline{OE}$ high deactivates the data output drivers (High-Z).                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 48,47,45,44,<br>42,41,40,38,<br>37,36,35,34,<br>32,31,29,28,<br>26,25 | Data Outputs                                    | Q <sub>17-0</sub> | Output       | 18 - bit wide output data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 60                                                                    | First Word Fall<br>Through/Serial<br>Data Input | FWFT/SDI          | Input        | Selects FWFT timing or Standard timing mode during Master<br>Reset. After Master Reset, if serial programming is selected<br>( $\overline{\text{LOAD}} = \text{high}$ ), FWFT/SDI is used as the serial data input for the<br>offset registers. Serial data is written during the low to high<br>transition of WCLK. Use in conjunction with $\overline{\text{SDEN}}$ .                                                                                                                                                                                                                                     |

**Table 1. Pin Descriptions**

| Pin #                        | Pin Name                           | Pin Symbol   | Input/Output | Description                                                                                                                                                                                                                                                                                                                                              |

|------------------------------|------------------------------------|--------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2                            | Serial Data<br>Input Enable        | SDEN         | Input        | If serial programming is selected, setting $\overline{\text{SDEN}}$ low<br>and $\overline{\text{LOAD}}$ low enables serial data input to be written<br>into offset registers during the low to high transition of<br>WCLK.                                                                                                                               |

| 50                           | Retransmit                         | RET          | Input        | Data previously read from the queue can be<br>retransmitted by asserting $\overline{\text{RET}}$ pin at the low to high<br>transition of RCLK for a retransmit operation.<br>Retransmit initializes the Read pointer to zero. Hence,<br>all re-reads will always start from the physical 0 <sup>th</sup><br>(Read pointer = zero) location of the queue. |

| 58                           | Full/Data Input<br>Ready Flag      | FULL / DRDY  | Output       | Queue is full when $\overline{\text{FULL}}$ goes low during the low to<br>high transition of WCLK. This prohibits further writes<br>into the queue. In FWFT mode, queue is full when<br>$\overline{\text{DRDY}}$ goes high during low to high transition of<br>WCLK. This prohibits further writes into the queue.                                       |

| 53                           | Empty/Data<br>Output Ready<br>Flag | EMPTY / QRDY | Output       | Queue is empty when $\overline{\text{EMPTY}}$ goes low during the low to high transition of RCLK. This prohibits further reads from the queue. In FWFT mode, queue is empty when $\overline{\text{QRDY}}$ goes high during the low to high transition of RCLK. This prohibits further reads from the queue.                                              |

| 57                           | Almost Full                        | PRAF         | Output       | Queue is almost full when $\overline{PRAF}$ goes low during the low to high transition of WCLK. Default (Full-offset) or programmed offset values determine the status of $\overline{PRAF}$ .                                                                                                                                                            |

| 54                           | Almost Empty                       | PRAE         | Output       | Queue is almost empty when $\overline{PRAE}$ goes low during<br>the low to high transition of RCLK. Default (Empty<br>+offset) or programmed offset values determine the<br>status of $\overline{PRAE}$ .                                                                                                                                                |

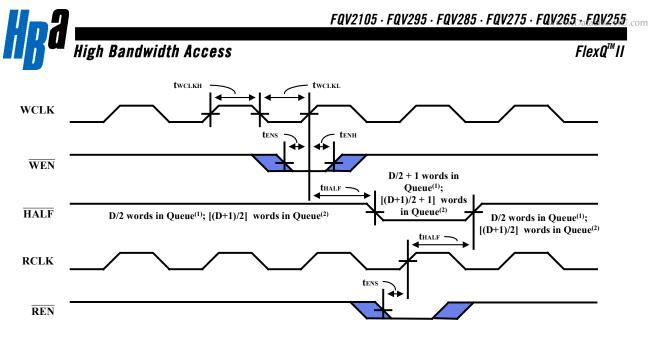

| 56                           | Half Full                          | HALF         | Output       | Queue is more than half full when $\overline{\text{HALF}}$ goes low.<br>Triggered by both WCLK and RCLK.                                                                                                                                                                                                                                                 |

| 3                            | Don't Care                         | DC           | N/A          | This pin can be tied high or low, cannot be left open.                                                                                                                                                                                                                                                                                                   |

| 4, 30, 43, 55                | Power                              | Vcc          | N/A          | 3.3V power supply.                                                                                                                                                                                                                                                                                                                                       |

| 5, 24, 27, 33, 39,<br>46, 57 | Ground                             | GND          | N/A          | 0V Ground.                                                                                                                                                                                                                                                                                                                                               |

Table 1. Pin Descriptions (Continued)

| Symbol | Rating                               | Com'l & Ind'l | Unit |

|--------|--------------------------------------|---------------|------|

| VTERM  | Terminal Voltage with respect to GND | -0.5 to +4.6  | V    |

| Tstg   | Storage Temperature                  | -55 to +125   | °C   |

| Iout   | DC Output Current                    | -50 to +50    | mA   |

## NOTES:

Absolute Max Ratings are for reference only. Permanent damage to the device may occur if extended period of operation is outside this range. Standard operation should fall within the Recommended Operating Conditions.

# Table 2. Absolute Maximum Ratings

|                       | Commercial<br>Clock = 7.5ns, 10ns, 15ns,<br>20ns |      |      | Clock = | Industria<br>7.5ns, 10<br>20ns |      |      |      |

|-----------------------|--------------------------------------------------|------|------|---------|--------------------------------|------|------|------|

| Symbol                | Parameter                                        | Min. | Тур. | Max.    | Min.                           | Тур. | Max. | Unit |

| Recommended O         | perating Conditions                              |      |      |         |                                |      |      |      |

| Vcc                   | Supply Voltage Com'l / Ind'l                     | 3.0  | 3.3  | 3.6     | 3.0                            | 3.3  | 3.6  | V    |

| GND                   | Supply Voltage                                   | 0    | 0    | 0       | 0                              | 0    | 0    | V    |

| VIH                   | Input High Voltage Com'l /<br>Ind'l              | 2.0  | -    | 5.0     | 2.0                            | -    | 5.0  | V    |

| VIL                   | Input Low Voltage Com'l /<br>Ind'l               | -    | -    | 0.8     | -                              | -    | 0.8  | V    |

| Та                    | Operating Temperature<br>Commercial              | 0    | -    | 70      | 0                              | -    | 70   | °C   |

| ТА                    | Operating Temperature<br>Industrial              | -40  | -    | 85      | -40                            | -    | 85   | °C   |

| DC Electrical Ch      | aracteristics                                    |      |      |         |                                |      |      |      |

| ILI <sup>(1)</sup>    | Input Leakage Current (any input)                | -10  | -    | 10      | -10                            | -    | 10   | μΑ   |

| Ilo                   | Output Leakage Current                           | -10  | -    | 10      | -10                            | -    | 10   | μΑ   |

| Voh                   | Output Logic "1" Voltage,<br>IOH=-2mA            | 2.4  | -    | -       | 2.4                            | -    | -    | V    |

| Vol                   | Output Logic "0" Voltage, IOL<br>= 8mA           | -    | -    | 0.4     | -                              | -    | 0.4  | V    |

| Power Consumpt        | tion                                             |      |      |         |                                |      |      |      |

| Icc1 <sup>(2,3)</sup> | Active Power Supply Current                      | -    | -    | 60      | -                              | -    | 60   | mA   |

| Icc2 <sup>(4)</sup>   | Standby Current                                  | -    | -    | 20      | -                              | -    | 20   | mA   |

**Table 3. DC Specifications**

| Capacitance at 100MHz Ambient Temperature (25°C) |                    |             |      |      |  |  |  |  |  |

|--------------------------------------------------|--------------------|-------------|------|------|--|--|--|--|--|

| Symbol                                           | Parameter          | Conditions  | Max. | Unit |  |  |  |  |  |

| CIN <sup>(2)</sup>                               | Input Capacitance  | $V_{IN}=0V$ | 10   | pF   |  |  |  |  |  |

| COUT <sup>(2,4)</sup>                            | Output Capacitance | VOUT= 0V    | 10   | pF   |  |  |  |  |  |

NOTES:

1. Measurement with 0.4<=VIN<=Vcc

2. With output tri-stated ( $\overline{OE} = High$ )

3. Icc(1,2) is measured with WCLK and RCLK at 20 MHz

4. Design simulated, not tested.

Table 3. DC Specifications (Continued)

|                | -                                                                                                     | Commercial & Industrial                                                           |      |                                                           |      |                                                                             |      |                                                                             |      |      |

|----------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|------|-----------------------------------------------------------|------|-----------------------------------------------------------------------------|------|-----------------------------------------------------------------------------|------|------|

|                |                                                                                                       | FQV2105-7.5<br>FQV295-7.5<br>FQV285-7.5<br>FQV275-7.5<br>FQV265-7.5<br>FQV255-7.5 |      | FQV295-7.5FQV295-10FQV285-7.5FQV285-10FQV275-7.5FQV275-10 |      | FQV2105-15<br>FQV295-15<br>FQV285-15<br>FQV275-15<br>FQV265-15<br>FQV255-15 |      | FQV2105-20<br>FQV295-20<br>FQV285-20<br>FQV275-20<br>FQV265-20<br>FQV255-20 |      |      |

| Symbol         | Parameter                                                                                             | Min.                                                                              | Max. | Min.                                                      | Max. | Min.                                                                        | Max. | Min.                                                                        | Max. | Unit |

| fs             | Clock Cycle Frequency                                                                                 | -                                                                                 | 133  | -                                                         | 100  | -                                                                           | 66   | -                                                                           | 50   | MHz  |

| tA             | Data Access Time                                                                                      | 1                                                                                 | 5    | 2                                                         | 6.5  | 2                                                                           | 10   | 2                                                                           | 12   | ns   |

| twclk          | Write Clock Cycle Time                                                                                | 7.5                                                                               | -    | 10                                                        | -    | 15                                                                          | -    | 20                                                                          | -    | ns   |

| twclkh         | Write Clock High Time                                                                                 | 3.5                                                                               | -    | 4.5                                                       | -    | 6                                                                           | -    | 8                                                                           | -    | ns   |

| twclkl         | Write Clock Low Time                                                                                  | 3.5                                                                               | -    | 4.5                                                       | -    | 6                                                                           | -    | 8                                                                           | -    | ns   |

| <b>t</b> rclk  | Read Clock Cycle Time                                                                                 | 7.5                                                                               | -    | 10                                                        | -    | 15                                                                          | -    | 20                                                                          | -    | ns   |

| <b>t</b> rclkh | Read Clock High Time                                                                                  | 3.5                                                                               | -    | 4.5                                                       | -    | 6                                                                           | -    | 8                                                                           | -    | ns   |

| <b>t</b> rclkl | Read Clock Low Time                                                                                   | 3.5                                                                               | -    | 4.5                                                       | -    | 6                                                                           | -    | 8                                                                           | -    | ns   |

| tos            | Data Set-up Time                                                                                      | 2.5                                                                               | -    | 3                                                         | -    | 4                                                                           | -    | 5                                                                           | -    | ns   |

| tон            | Data Hold Time                                                                                        | 0.5                                                                               | -    | 0.5                                                       | -    | 1                                                                           | -    | 1                                                                           | -    | ns   |

| tens           | Enable Set-up Time                                                                                    | 2.5                                                                               | -    | 3                                                         | -    | 4                                                                           | -    | 1                                                                           | -    | ns   |

| tenh           | Enable Hold Time                                                                                      | 0.5                                                                               | -    | 0.5                                                       | -    | 1                                                                           | -    | 1                                                                           | -    | ns   |

| <b>t</b> rst   | Reset Pulse Width <sup>(1)</sup>                                                                      | 10                                                                                | -    | 10                                                        | -    | 15                                                                          | -    | 20                                                                          | -    | ns   |

| trsts          | Reset Set-up Time                                                                                     | 10                                                                                |      | 10                                                        | -    | 15                                                                          | -    | 20                                                                          | -    | ns   |

| <b>t</b> rstr  | Reset Recovery Time                                                                                   | 10                                                                                | -    | 10                                                        | -    | 15                                                                          | -    | 20                                                                          | -    | ns   |

| <b>t</b> rstf  | Reset to Flag and Output Time                                                                         | -                                                                                 | 10   | -                                                         | 10   | -                                                                           | 15   | -                                                                           | 20   | ns   |

| trets          | Retransmit Setup Time                                                                                 | 2.5                                                                               | -    | 3                                                         | -    | 4                                                                           | -    | 5                                                                           | -    | ns   |

| tolz           | Output Enable to Output in Low-Z <sup>(1)</sup>                                                       | 0                                                                                 | -    | 0                                                         | -    | 0                                                                           | -    | 0                                                                           | -    | ns   |

| toe            | Output Enable to Output Valid                                                                         | 2                                                                                 | 5    | 2                                                         | 6    | 3                                                                           | 8    | 3                                                                           | 10   | ns   |

| tонz           | Output Enable to Output in High-Z <sup>(1)</sup>                                                      | 2                                                                                 | 5    | 2                                                         | 6    | 3                                                                           | 8    | 3                                                                           | 10   | ns   |

| <b>t</b> full  | Write Clock to Full Flag                                                                              | -                                                                                 | 5    | -                                                         | 6.5  | -                                                                           | 10   | -                                                                           | 12   | ns   |

| <b>t</b> empty | Read Clock to Empty Flag                                                                              | -                                                                                 | 5    | -                                                         | 6.5  | -                                                                           | 10   | -                                                                           | 12   | ns   |

| <b>t</b> PRAFS | Write Clock to Almost-Full Flag                                                                       | -                                                                                 | 5    | -                                                         | 6.5  | -                                                                           | 10   | -                                                                           | 12   | ns   |

| <b>t</b> PRAES | Read Clock to Almost-Empty Flag                                                                       | -                                                                                 | 5    | -                                                         | 6.5  | -                                                                           | 10   | -                                                                           | 12   | ns   |

| <b>t</b> skew1 | Skew time between Read Clock &<br>Write Clock for Full Flag / Empty Flag                              | 4                                                                                 | -    | 5                                                         | -    | 6                                                                           | -    | 10                                                                          | -    | ns   |

| tskew2         | Skew time between Read Clock &<br>Write Clock for $\overline{\text{PRAF}}$ & $\overline{\text{PRAE}}$ | 7                                                                                 | -    | 12                                                        | -    | 15                                                                          | -    | 20                                                                          | -    | ns   |

**Table 4. AC Electrical Characteristics**

|                |                       |             | Commercial & Industrial |                          |       |            |       |            |       |      |

|----------------|-----------------------|-------------|-------------------------|--------------------------|-------|------------|-------|------------|-------|------|

|                |                       | FQV2105-7.5 |                         | FQV2105-7.5 FQV2105-10 I |       | FQV2105-15 |       | FQV2105-20 |       |      |

|                |                       | FQV295-7.5  |                         | FQV2                     | 95-10 | FQV2       | 95-15 | FQV2       | 95-20 |      |

|                |                       | FQV285-7.5  |                         | FQV285-7.5 FQV285-10     |       | FQV285-15  |       | FQV285-20  |       |      |

|                |                       | FQV275-7.5  |                         |                          |       | FQV275-15  |       | FQV275-20  |       |      |

|                |                       | FQV265-7.5  |                         |                          |       | FQV265-15  |       | FQV265-20  |       |      |

|                |                       | FQV255-7.5  |                         | FQV255-7.5 FQV255-10     |       | FQV255-15  |       | FQV255-20  |       |      |

| Symbol         | Parameter             | Min.        | Max.                    | Min.                     | Max.  | Min.       | Max.  | Min.       | Max.  | Unit |

| tloads         | Load Setup Time       | 2.5         | -                       | 3                        | -     | 4          | -     | 5          | -     | ns   |

| <b>t</b> loadh | Load Hold Time        | 0.5         | -                       | 0.5                      | -     | 1          | -     | 1          | -     | ns   |

| <b>t</b> rts   | Retransmit Setup Time | 3           | -                       | 3                        | -     | 4          | -     | 5          | -     | ns   |

| thf            | Clock to HALF         | -           | 14                      | -                        | 16    | -          | 20    | -          | 22    | ns   |

# NOTES:

1. Design simulated, not tested.

Table 4. AC Electrical Characteristics (Continued)

| Input Pulse Levels                                  | GND to 3.0V       |

|-----------------------------------------------------|-------------------|

| Input Rise/Fall Times                               | 3ns               |

| Input Timing Reference Levels                       | 1.5V              |

| Output Reference Levels                             | 1.5V              |

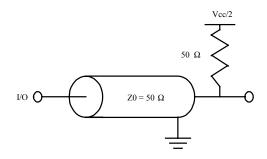

| Output Load, clock = 7.5 ns                         | Refer to Figure 4 |

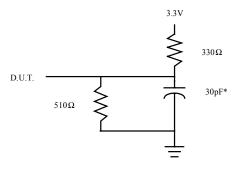

| Output Load <sup>*</sup> , clock = 10ns, 15ns, 20ns | Refer to Figure 5 |

\* Include jig and scope capacitances

Table 5. AC Test Condition

Figure 4. AC Test Load for clock = 7.5ns

Figure 5. Output Load for clock = 10ns, 15ns, 20ns \*Includes jig and scope capacitances.

# **Pin Functions**

| MRST              | Master Reset is required to initialize Write and Read pointers to the first position of the queue by setting $\overline{\text{MRST}}$ low. In Standard mode, $\overline{\text{FULL}}$ and $\overline{\text{PRAF}}$ will go high; $\overline{\text{EMPTY}}$ and $\overline{\text{PRAE}}$ will go low. In FWFT mode, $\overline{\text{DRDY}}$ will go low and $\overline{\text{QRDY}}$ will go high. $\overline{\text{PRAF}}$ and $\overline{\text{PRAE}}$ will go to the same state as Standard mode. In both modes, all data outputs will go low. Previous programmed configurations will not be maintained.                                                                                                                                                                                 |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PRST              | Partial Reset is required to initialize Write and Read pointers to the first position of the queue by setting $\overrightarrow{PRST}$ low. In Standard mode, $\overrightarrow{FULL}$ and $\overrightarrow{PRAF}$ will go high; $\overrightarrow{EMPTY}$ and $\overrightarrow{PRAE}$ will go low. In FWFT mode, $\overrightarrow{DRDY}$ will go low and $\overrightarrow{QRDY}$ will go high. $\overrightarrow{PRAF}$ and $\overrightarrow{PRAE}$ will go to the same state as Standard mode. In both modes, all data outputs will go low. Previous programmed configurations will be maintained.                                                                                                                                                                                             |

| WCLK              | Writes data into queue during low to high transitions of WCLK if $\overline{WEN}$ is activated. Synchronizes $\overline{FULL} / \overline{DRDY}$ and $\overline{PRAF}$ flags. WCLK and RCLK are independent of each other.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| WEN               | Controls write operation into queue or offset registers during low to high transition of WCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

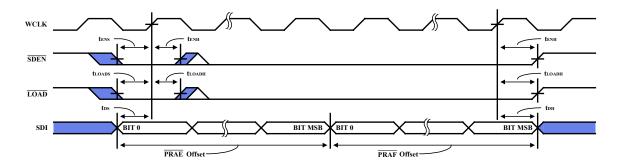

| LOAD              | During Master Reset, set $\overline{\text{LOAD}}$ low to select parallel programming or one of eight default offset values. Set $\overline{\text{LOAD}}$ high to select serial programming or one of eight default offset values. After Master Reset, $\overline{\text{LOAD}}$ controls write/read, to/from offset registers during low to high transition of WCLK/RCLK respectively for parallel programming. Use in conjunction with $\overline{\text{WEN}} / \overline{\text{REN}}$ . During programming of offset registers, $\overline{\text{PRAF}}$ and $\overline{\text{PRAE}}$ flag status is invalid. For Serial programming, $\overline{\text{LOAD}}$ is used to enable serial loading of offset registers together with $\overline{\text{SDEN}}$ . Refer to Figure 6 for details. |

| D <sub>17-0</sub> | 18 - bit wide input data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RCLK              | Reads data from queue during low to high transitions of RCLK if $\overline{\text{REN}}$ is set low. Synchronizes the $\overline{\text{EMPTY}} / \overline{\text{QRDY}}$ and $\overline{\text{PRAE}}$ flags. RCLK and WCLK are independent of each other.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| REN               | Reads data from queue during low to high transitions of RCLK if $\overline{\text{REN}}$ is set to low. This also advances the Read pointer of the queue.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ŌĒ                | Setting $\overline{OE}$ low activates the data output drivers. Setting $\overline{OE}$ high deactivates the data output drivers (High-Z). $\overline{OE}$ does not control advancement of Read pointer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Q <sub>17-0</sub> | 18 - bit wide output data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| FWFT/SDI          | Selects FWFT timing or Standard timing mode during Master Reset. After Master Reset, if serial programming is selected ( $\overline{LOAD} = high$ ), FWFT/SDI is used as the serial data input for the offset registers. Serial data is written during the low to high transition of WCLK. Use in conjunction with $\overline{SDEN}$ . In FWFT mode, $\overline{DRDY}$ and $\overline{QRDY}$ is used instead of $\overline{FULL}$ and $\overline{EMPTY}$ . Refer to Table 10 for all flags status. In Standard mode, $\overline{FULL}$ and $\overline{EMPTY}$ are used instead of $\overline{DRDY}$ and $\overline{QRDY}$ . Refer to Table 9 for all flags status.                                                                                                                           |

| <b>SDEN</b>       | If serial programming is selected, setting $\overline{\text{SDEN}}$ and $\overline{\text{LOAD}}$ low enables serial data to be written<br>into offset registers during the low to high transition of WCLK. During serial programming,<br>$\overline{\text{PRAF}}$ and $\overline{\text{PRAE}}$ flags status is invalid. Refer to Figure 6 for details.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| RET               | Data previously read from the queue can be retransmitted by asserting $\overline{\text{RET}}$ pin at the low to high transition of RCLK for a retransmit operation. Retransmit initializes the Read pointer to zero. Hence, all re-reads will always start from the physical 0 <sup>th</sup> (Read pointer = zero), location of the queue. Refer to Diagram 7 & 8 for details.                                                                                                                                                                                                                                                                                                                                                                                                               |

# **Pin Functions (Continued)**

| FULL / DRDY  | In Standard mode, queue is full when $\overline{FULL}$ goes low during the low to high transition of WCLK.<br>This prohibits further writes into the queue and prevents advancement of Write pointer. In FWFT mode, queue is full when $\overline{DRDY}$ goes high during the low to high transition of WCLK. This prohibits further writes into the queue and prevents advancement of Write pointer. Refer to Table 8 & 9 for behavior of $\overline{FULL}/\overline{DRDY}$ .                           |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EMPTY / QRDY | In Standard mode, queue is empty when $\overline{\text{EMPTY}}$ goes low during the low to high transition of RCLK. This prohibits further reads from the queue and prevents advancement of Read pointer. In FWFT mode, queue is empty when $\overline{\text{QRDY}}$ goes low during the low to high transition of RCLK. This prohibits further reads from the queue and prevents advancement of Read pointer. Refer to Table 8 & 9 for behavior of $\overline{\text{EMPTY}} / \overline{\text{QRDY}}$ . |

| PRAF         | In Synchronous mode, queue is almost full when $\overline{PRAF}$ goes low during the low to high transition of WCLK. Default (Full-offset) or programmed offset values determine the status of $\overline{PRAF}$ . In Asynchronous timing mode, $\overline{PRAF}$ is triggered by both WCLK and RCLK. Refer to Table 8 & 9 for behavior of $\overline{PRAF}$ .                                                                                                                                           |

| PRAE         | In Synchronous mode, queue is almost empty when $\overline{PRAE}$ goes low during the low to high transition of RCLK. Default (Empty+offset) or programmed offset values determine the status of $\overline{PRAE}$ . In Asynchronous timing mode, $\overline{PRAF}$ is triggered by both WCLK and RCLK. Refer to Table 8 & 9 for behavior of $\overline{PRAE}$ .                                                                                                                                         |

| HALF         | Queue is more than half full when $\overline{\text{HALF}}$ goes low during the low to high transition of WCLK.<br>$\overline{\text{HALF}}$ goes high during low to high transition of RCLK when queue is less than half full. Refer to Table 8 & 9 for details.                                                                                                                                                                                                                                          |

| LOAD | WEN | REN | SDEN | WCLK | RCLK | FQV2105<br>FQV295<br>FQV285<br>FQV275<br>FQV265<br>FQV255<br>Selection / Sequence                                                                                                                                                                                                                            |

|------|-----|-----|------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | 0   | 1   | 1    |      | Х    | Write to offset registers:Parallel write toEmpty Offsetregisters:Full Offset1. PRAE2. PRAF-                                                                                                                                                                                                                  |

| 0    | 1   | 0   | 1    | Х    |      | Read from offset registers:Parallel read from<br>registers:Empty Offset1. PRAE<br>2. PRAF                                                                                                                                                                                                                    |

| 0    | 1   | 1   | 0    |      | х    | Serial shift into registers:<br>36 bits for the FQV2105<br>34 bits for the FQV295<br>32 bits for the FQV285<br>30 bits for the FQV275<br>28 bits for the FQV265<br>26 bits for the FQV255<br>1 bit for each rising WCLK edge<br>Starting with Empty Offset (Low Byte)<br>Ending with Full Offset (High Byte) |

| Х    | 1   | 1   | 1    | Х    | Х    | No Operation                                                                                                                                                                                                                                                                                                 |

| 1    | 0   | Х   | Х    |      | Х    | Write Memory                                                                                                                                                                                                                                                                                                 |

| 1    | Х   | 0   | Х    | Х    |      | Read Memory                                                                                                                                                                                                                                                                                                  |

| 1    | 1   | 1   | Х    | Х    | Х    | No Operation                                                                                                                                                                                                                                                                                                 |

Figure 6. Programmable Flag Offset Programming Sequence

| Device  | <b>PRAF</b> P       | rogramming (bits)                                                        | <b>PRAE</b> Pr      | ogramming (bits)                                                       |

|---------|---------------------|--------------------------------------------------------------------------|---------------------|------------------------------------------------------------------------|

| FQV2105 | $D/Q_{15-0}$        | Low Word                                                                 | $D/Q_{15-0}$        | Low Word                                                               |

| 1012105 | D/Q <sub>1-0</sub>  | High Word                                                                | D/Q <sub>1-0</sub>  | High Word                                                              |

| FOV295  | D/Q <sub>15-0</sub> | Low Word                                                                 | D/Q <sub>15-0</sub> | Low Word                                                               |

| 101255  | D/Q <sub>0</sub>    | High Word                                                                | D/Q <sub>0</sub>    | High Word                                                              |

| FQV285  | D/Q <sub>15-0</sub> |                                                                          | D/Q <sub>15-0</sub> |                                                                        |

| FQV275  | D/Q <sub>14-0</sub> |                                                                          | D/Q <sub>14-0</sub> |                                                                        |

| FQV265  | D/Q <sub>13-0</sub> |                                                                          | D/Q <sub>13-0</sub> |                                                                        |

| FQV255  | D/Q <sub>12-0</sub> |                                                                          | D/Q <sub>12-0</sub> |                                                                        |

| ALL     | -                   | when $\overline{\text{LOAD}} = 0$<br>, when $\overline{\text{LOAD}} = 1$ |                     | when $\overline{\text{LOAD}} = 0$<br>when $\overline{\text{LOAD}} = 1$ |

Table 6. Parallel Offset Register Data Mapping and Default Values (DV) Table

| Device  | Standard Mode | FWFT         |

|---------|---------------|--------------|

| FQV2105 | 262,144 x 18  | 262,145 x 18 |

| FQV295  | 131,072 x 18  | 131,073 x 18 |

| FQV285  | 65,536 x 18   | 65,537 x 18  |

| FQV275  | 32,768 x 18   | 32,769 x 18  |

| FQV265  | 16,384 x 18   | 16,385 x 18  |

| FQV255  | 8,192 x 18    | 8,193 x 18   |

Table 7. Maximum Depth of Queue for Standard and FWFT Mode

| High Band                   | lwidth | Acces                  | s        |        |        |        |                 |      |               |        |               |      |      |             |             |                        | Flext       |

|-----------------------------|--------|------------------------|----------|--------|--------|--------|-----------------|------|---------------|--------|---------------|------|------|-------------|-------------|------------------------|-------------|

|                             |        |                        |          |        |        |        |                 |      |               |        |               |      |      |             |             |                        |             |

| Data Width                  | D/Q17  | D/Q16 D/Q1             | 5 D/Q14  | D/Q13  | D/Q12  | D/Q11  | D/Q10           | D/Q9 | D/Q8          | D/Q7   | D/Q6          | D/Q5 | D/Q4 | D/Q3        | D/Q2        | D/Q1                   | D/Q0        |

|                             |        |                        |          |        |        |        |                 |      |               |        |               |      |      |             |             |                        |             |

| st Cycle PRAE               |        | 15                     | 14       | 13     | 12     | 11     | 10              | 9    | 8             | 7      | 6             | 5    | 4    | 3           | 2           | 1                      | 0           |

| d Cycle PRAF                |        | 15                     | 14       | 13     | 12     | 11     | 10              | 9    | 8             | 7      | 6             | 5    | 4    | 3           | 2           | 1                      | 0           |

|                             |        |                        |          |        |        |        | QV27            |      |               |        |               |      |      |             |             |                        |             |

|                             |        |                        |          | Parall | el Ofi | fset V | Vrite/          | Read | Cycle         | es for | x18 V         |      |      |             |             |                        |             |

| Data Width                  | D/Q17  | D/Q16 D/Q              |          | Parall | el Ofi | fset V | Vrite/          | Read | Cycle         | es for | x18 V         |      |      | D/Q3        | D/Q2        | D/Q1                   | D/Q0        |

| Data Width<br>st Cycle PRAE | D/Q17  | <b>D/Q16 D/Q</b><br>15 |          | Parall | el Ofi | fset V | Vrite/          | Read | Cycle         | es for | x18 V         |      |      | <b>D/Q3</b> | <b>D/Q2</b> | <b>D/Q1</b>            | <b>D/Q0</b> |

| st Cycle PRAE               | D/Q17  |                        | 15 D/Q14 | Parall | el Ofi | fset W | Vrite/<br>D/Q10 | Read | Cycle<br>D/Q8 | D/Q7   | x18 V<br>D/Q6 | D/Q5 | D/Q4 | 1           |             | <b>D/Q1</b><br>1<br>17 |             |

|                             |        |                        | 15 D/Q14 | Parall | el Ofi | fset W | Vrite/<br>D/Q10 | Read | Cycle<br>D/Q8 | D/Q7   | x18 V<br>D/Q6 | D/Q5 | D/Q4 | 1           |             | 1                      | 0           |

FQV2105, FQV295 Parallel Offset Write/Read Cycles for x18 Width

| # of Bits for Offset Registers              |  |  |  |  |  |  |

|---------------------------------------------|--|--|--|--|--|--|

| 18 bits for FQV2105                         |  |  |  |  |  |  |

| 17 bits for FQV295                          |  |  |  |  |  |  |

| 16 bits for FQV285                          |  |  |  |  |  |  |

| 15 bits for FQV275                          |  |  |  |  |  |  |

| 14 bits for FQV265                          |  |  |  |  |  |  |

| 13 bits for FQV255                          |  |  |  |  |  |  |

| Note: Don't Care applies to all unused bits |  |  |  |  |  |  |

Figure 7. Parallel Offset Write/Read Cycles Diagram

Η

Η

131,072

FlexQ<sup>™</sup>II

| FQV2105                                                                              | FULL                | PRAF             | HALF      | PRAE                       | EMPTY                |

|--------------------------------------------------------------------------------------|---------------------|------------------|-----------|----------------------------|----------------------|

| 0                                                                                    | Н                   | Н                | Н         | L                          | L                    |

| 1 to $y^{(1)}$                                                                       | Н                   | Н                | Н         | L                          | Н                    |

| (y+1) to 131,072                                                                     | Н                   | Н                | Н         | Н                          | Н                    |

| 131,073 to [262,144-(x+1)]                                                           | Н                   | Н                | L         | Н                          | Н                    |

| $(262,144-x^{(2)})$ to 262,143                                                       | Н                   | L                | L         | Н                          | Н                    |

|                                                                                      | ~                   | Ŧ                | т         | 11                         | TT                   |

| 262,144                                                                              | L                   | L                | L         | Н                          | Н                    |

| 262,144                                                                              | L                   | L                | L         | Н                          | Н                    |

| 262,144<br>FQV295                                                                    | L     FULL          | L <b>PRAF</b>    | L<br>HALF | H<br>PRAE                  | H<br>EMPTY           |

| <b>FQV295</b><br>0                                                                   | ·                   | ·                | HALF<br>H |                            |                      |

| ,                                                                                    | FULL                | PRAF             |           |                            | EMPTY                |

| <b>FQV295</b><br>0                                                                   | <b>FULL</b><br>H    | <b>PRAF</b><br>H | Н         |                            | EMPTY<br>L           |

| FQV295<br>0<br>1 to y <sup>(1)</sup><br>(y+1) to 65,536<br>65,537 to [131,072-(x+1)] | FULL     H     H    | PRAF   H   H     | H<br>H    | <b>PRAE</b><br>L<br>L      | EMPTY<br>L<br>H      |

| <b>FQV295</b><br>0<br>1 to y <sup>(1)</sup><br>(y+1) to 65,536                       | FULL<br>H<br>H<br>H | PRAFHHH          | H<br>H    | <b>PRAE</b><br>L<br>L<br>H | EMPTY<br>L<br>H<br>H |

L

L

L

| FQV285                         | FULL | PRAF | HALF | PRAE | EMPTY |

|--------------------------------|------|------|------|------|-------|

| 0                              | Н    | Н    | Н    | L    | L     |

| 1 to $y^{(1)}$                 | Н    | Н    | Н    | L    | Н     |

| (y+1) to 32,768                | Н    | Н    | Н    | Н    | Н     |

| 32,769 to [65,536-(x+1)]       | Н    | Н    | L    | Н    | Н     |

| $(65,536-x^{(2)})$ to $65,535$ | Н    | L    | L    | Н    | Н     |

| 65,536                         | L    | L    | L    | Н    | Н     |

| FQV275                       | FULL | PRAF | HALF | PRAE | EMPTY |

|------------------------------|------|------|------|------|-------|

| 0                            | Н    | Н    | Н    | L    | L     |

| 1 to $y^{(1)}$               | Н    | Н    | Н    | L    | Н     |

| (y+1) to 16,384              | Н    | Н    | Н    | Н    | Н     |

| 16,385 to [32,768-(x+1)]     | Н    | Н    | L    | Н    | Н     |

| $(32,768-x^{(2)})$ to 32,767 | Н    | L    | L    | Н    | Н     |

| 32,768                       | L    | L    | L    | Н    | Н     |

| FQV265                         | FULL | PRAF | HALF | PRAE | EMPTY |

|--------------------------------|------|------|------|------|-------|

| 0                              | Н    | Н    | Н    | L    | L     |

| 1 to $y^{(1)}$                 | Н    | Н    | Н    | L    | Н     |

| (y+1) to 8,192                 | Н    | Н    | Н    | Н    | Н     |

| 8,193 to [16,384-(x+1)]        | Н    | Н    | L    | Н    | Н     |

| $(16,384 - x^{(2)})$ to 16,383 | Н    | L    | L    | Н    | Н     |

| 16,384                         | L    | L    | L    | Н    | Н     |

| FQV255                       | FULL | PRAF | HALF | PRAE | EMPTY |

|------------------------------|------|------|------|------|-------|

| 0                            | Н    | Н    | Н    | L    | L     |

| 1 to $y^{(1)}$               | Н    | Н    | Н    | L    | Н     |

| (y+1) to 4,096               | Н    | Н    | Н    | Н    | Н     |

| 4,097 to [8,192-(x+1)]       | Н    | Н    | L    | Н    | Н     |

| $(8,192-x^{(2)})$ to $8,191$ | Н    | L    | L    | Н    | Н     |

| 8,192                        | L    | L    | L    | Н    | Н     |

NOTES:

- 1.  $y = \overline{PRAE}$  offset; Default Values: y = 127 when parallel offset loading is selected or y = 1,023 when serial offset loading is selected.

- 2.  $x = \overline{PRAF}$  offset; Default Values: x = 127 when parallel offset loading is selected or x = 1,023 when serial offset loading is selected.

Table 8. Status Flags (Standard Mode)

| FQV2105                        | DRDY | PRAF | HALF | PRAE | QRDY |

|--------------------------------|------|------|------|------|------|

| 0                              | L    | Н    | Н    | L    | Н    |

| 1 to $y^{(1)}+1$               | L    | Н    | Н    | L    | L    |

| (y+2) to 131,073               | L    | Н    | Н    | Н    | L    |

| 131,074 to [262,145-(x+1)]     | L    | Н    | L    | Н    | L    |

| $(262,145-x^{(2)})$ to 262,144 | L    | L    | L    | Н    | L    |

| 262,145                        | Н    | L    | L    | Н    | L    |

| FQV295                         | DRDY | PRAF | HALF | PRAE | QRDY |

|--------------------------------|------|------|------|------|------|

| 0                              | L    | Н    | Н    | L    | Н    |

| 1 to $y^{(1)}+1$               | L    | Н    | Н    | L    | L    |

| (y+2) to 65,537                | L    | Н    | Н    | Н    | L    |

| 65,538 to [131,073-(x+1)]      | L    | Н    | L    | Н    | L    |

| $(131,073-x^{(2)})$ to 131,072 | L    | L    | L    | Н    | L    |

| 131,073                        | Н    | L    | L    | Н    | L    |

| FQV285                         | DRDY | PRAF | HALF | PRAE | QRDY |

|--------------------------------|------|------|------|------|------|

| 0                              | L    | Н    | Н    | L    | Н    |

| 1 to $y^{(1)}+1$               | L    | Н    | Н    | L    | L    |

| (y+2) to 32,769                | L    | Н    | Н    | Н    | L    |

| 32,770 to [65,537-(x+1)]       | L    | Н    | L    | Н    | L    |

| $(65,537-x^{(2)})$ to $65,536$ | L    | L    | L    | Н    | L    |

| 65,537                         | Н    | L    | L    | Н    | L    |

| FQV275                       | DRDY | PRAF | HALF | PRAE | QRDY |

|------------------------------|------|------|------|------|------|

| 0                            | L    | Н    | Н    | L    | Н    |

| 1 to $y^{(1)}+1$             | L    | Н    | Н    | L    | L    |

| (y+2) to 16,385              | L    | Н    | Н    | Н    | L    |

| 16,386 to [32,769-(x+1)]     | L    | Н    | L    | Н    | L    |

| $(32,769-x^{(2)})$ to 32,768 | L    | L    | L    | Н    | L    |

| 32,769                       | Н    | L    | L    | Н    | L    |

| FQV265                         | DRDY | PRAF | HALF | PRAE | QRDY |

|--------------------------------|------|------|------|------|------|

| 0                              | L    | Н    | Н    | L    | Н    |

| 1 to $y^{(1)}+1$               | L    | Н    | Н    | L    | L    |

| (y+2) to 8,193                 | L    | Н    | Н    | Н    | L    |

| 8,194 to [16,385-(x+1)]        | L    | Н    | L    | Н    | L    |

| $(16,385 - x^{(2)})$ to 16,384 | L    | L    | L    | Н    | L    |

| 16,385                         | Н    | L    | L    | Н    | L    |

| FQV255                       | DRDY | PRAF | HALF | PRAE | QRDY |

|------------------------------|------|------|------|------|------|

| 0                            | L    | Н    | Н    | L    | Н    |

| 1 to $y^{(1)}+1$             | L    | Н    | Н    | L    | L    |

| (y+2) to 4,097               | L    | Н    | Н    | Н    | L    |

| 4,098 to [8,193-(x+1)]       | L    | Н    | L    | Н    | L    |

| $(8,193-x^{(2)})$ to $8,192$ | L    | L    | L    | Н    | L    |

| 8,193                        | Н    | L    | L    | Н    | L    |

#### NOTES:

1.  $y = \overline{PRAE}$  offset; Default Values: y = 127 when parallel offset loading is selected or y = 1,023 when serial offset loading is selected. 2.  $x = \overline{PRAF}$  offset; Default Values: x = 127 when parallel offset loading is selected or x = 1,023 when serial offset loading is selected.

Table 9. Status Flags (FWFT Mode)

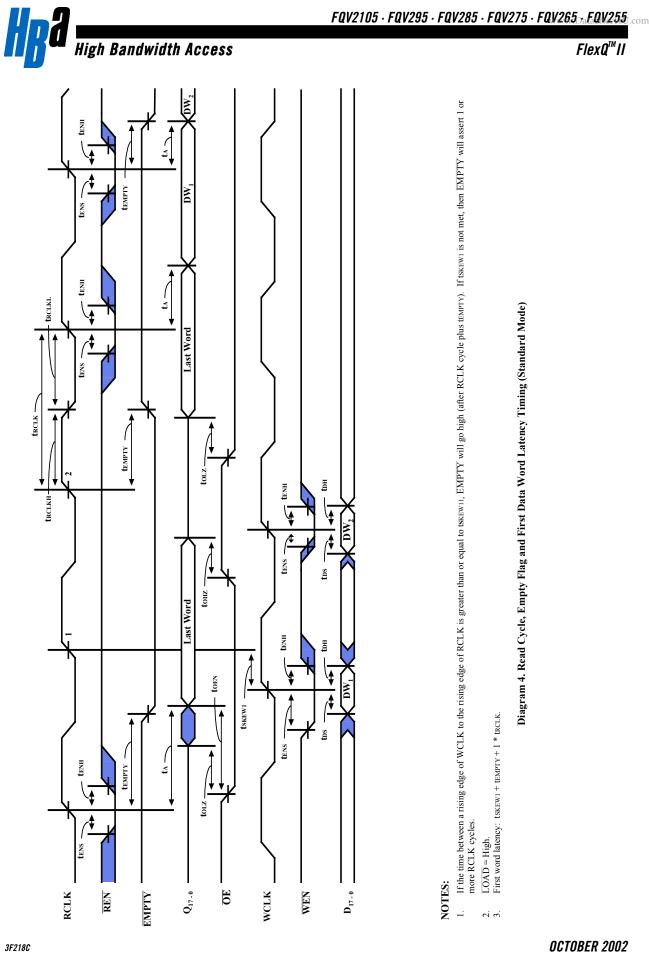

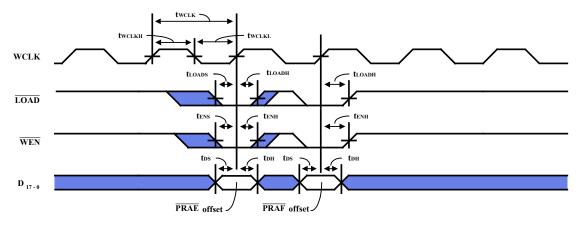

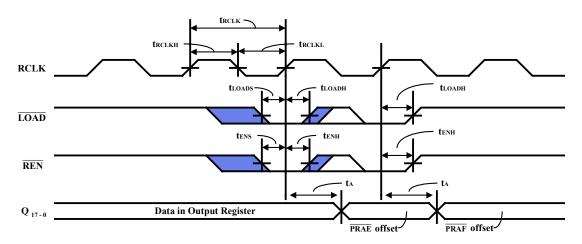

# **Timing Diagrams**

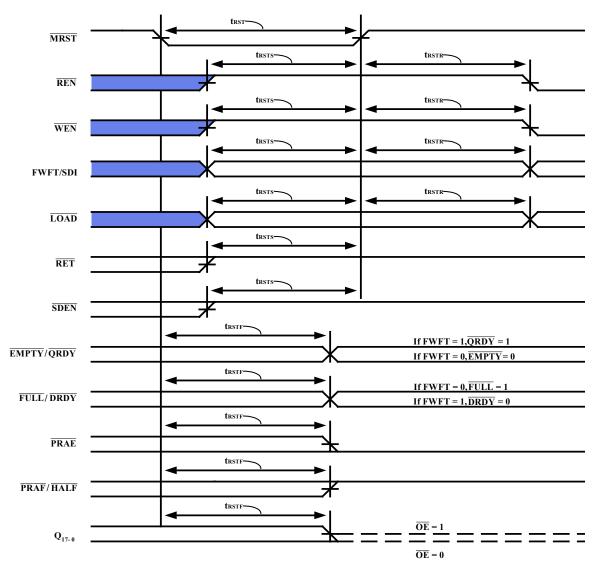

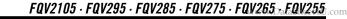

Diagram 1. Master Reset Timing

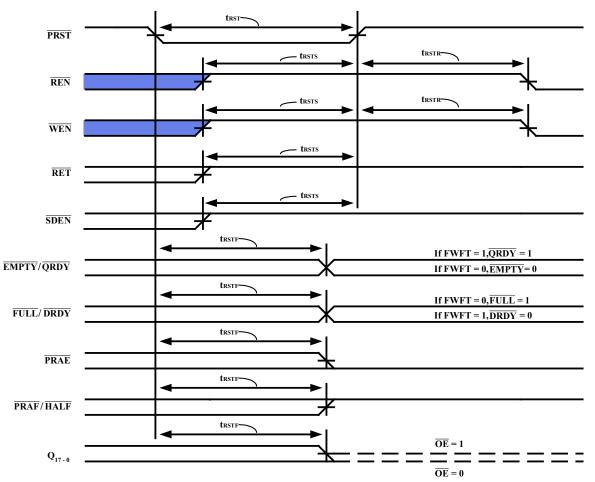

**Diagram 2. Partial Reset Timing**

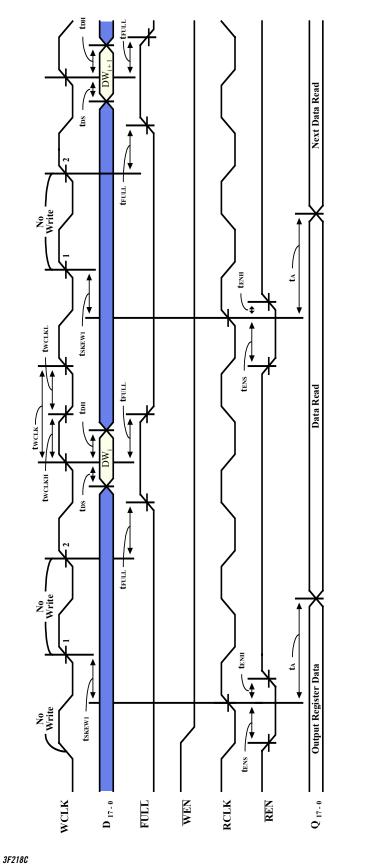

# NOTES:

- If the time between a rising edge of RCLK to the rising edge of WCLK is greater than or equal to tskew1, FULL will go high (after one WCLK cycle plus tFULL). If tskEw1 is not met, then FULL will assert 1 or more WCLK cycles.

- 2.  $\underline{\text{LOAD}} = \text{High}, \overline{\text{OE}} = \text{Low}.$

# Diagram 3. Write Cycle and Full Flag Timing (Standard Mode)

OCTOBER 2002 www.pataShget4U.com

© 2001 High Bandwidth Access, Inc. All rights reserved. Product specifications subject to change without notice.

© 2001 High Bandwidth Access, Inc. All rights reserved. Product specifications subject to change without notice.

www.DataSheet4U.com

© 2001 High Bandwidth Access, Inc. All rights reserved. Product specifications subject to change without notice.

UCIUBER 2002 www.DataSheet4U.com

<sup>© 2001</sup> High Bandwidth Access, Inc. All rights reserved. Product specifications subject to change without notice.

<u>UCIUBER 2002</u> www.DataSheet4U.com

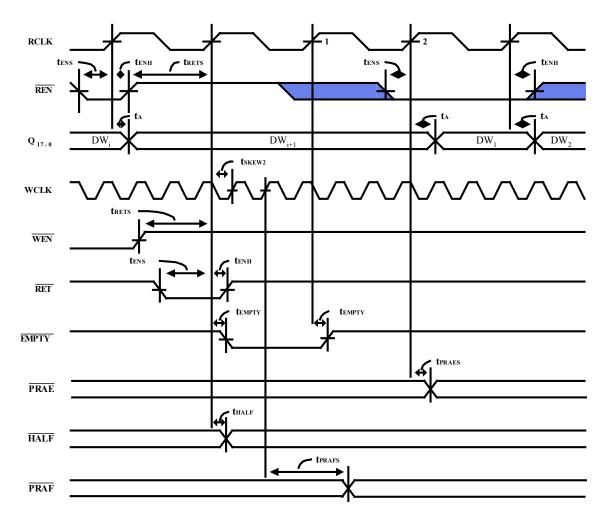

# NOTES:

- <u>Upon</u> completion of retransmit setup, a read operation can begin only after  $\overline{\text{EMPTY}}$  returns high.  $\overline{\text{OE}} = \text{Low}.$ 1.

- 2.

- $DW_i = Words$  written to the queue after  $\overline{MRST}$ . Where i = 1,2,3... depth. 3.

- 4. Upon reset completion, there must be more than 2 words written to the queue for a retransmit setup to be valid.

Diagram 7. Retransmit Timing (Standard Mode)

### NOTES:

- Upon completion of retransmit setup, a read operation can begin only after QRDY returns low. 1.

- 2.  $\overline{OE} = Low.$

- 3.

- $\overline{\text{DW}}_{i} = W \text{ords}$  written to the queue after  $\overline{\text{MRST}}$ . Where i = 1, 2, 3... depth. Upon reset completion, there must be more than 2 words written to the queue for a retransmit setup to be valid. 4.

- 5. Please refer to Table 7 for Depth.

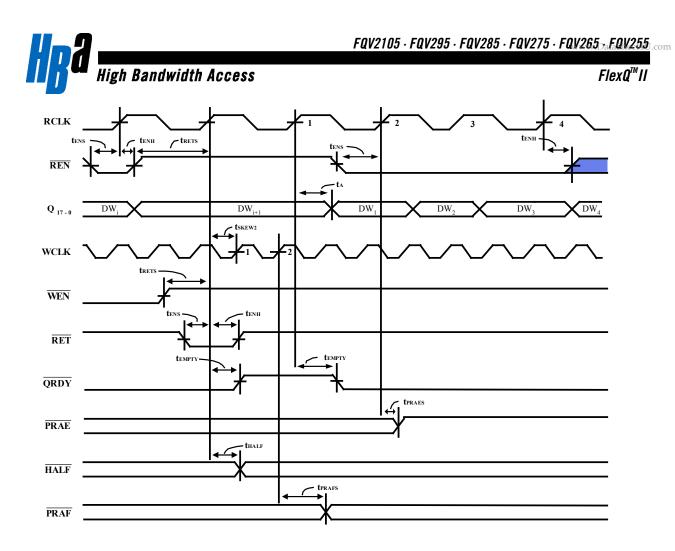

Diagram 8. Retransmit Timing (FWFT Mode)

\* Refer to Table 10.

|     | FQV2105 | FQV295 | FQV285 | FQV275 | FQV265 | FQV255 |

|-----|---------|--------|--------|--------|--------|--------|

| MSB | 17      | 16     | 15     | 14     | 13     | 12     |

Table 10. Reference Table for Diagram 9

Diagram 10. Parallel Loading of Programmable Flag Registers (Standard and FWFT Mode)

Diagram 11. Parallel Read of Programmable Flag Registers (Standard and FWFT Mode)

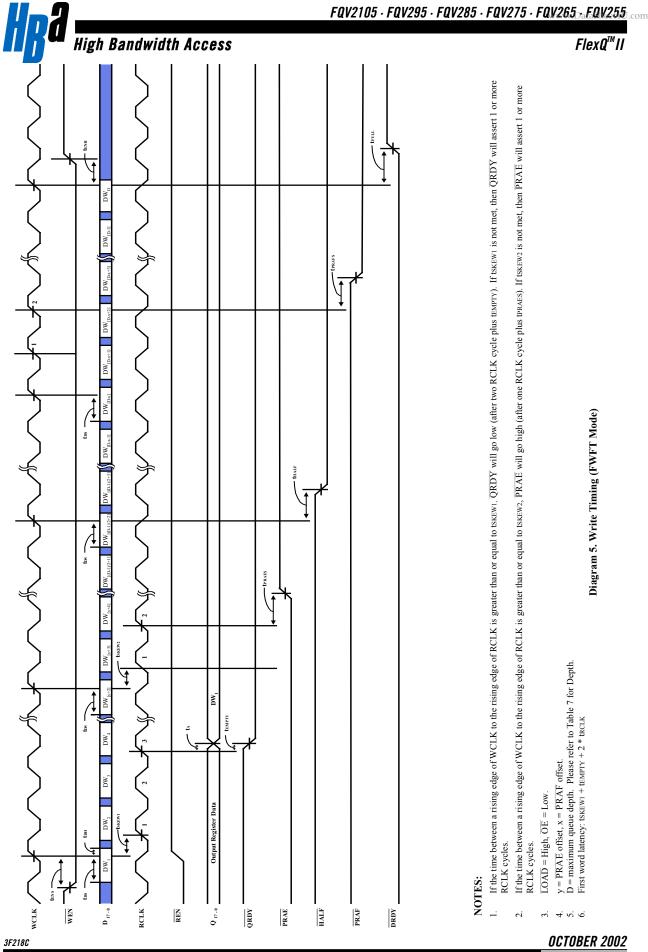

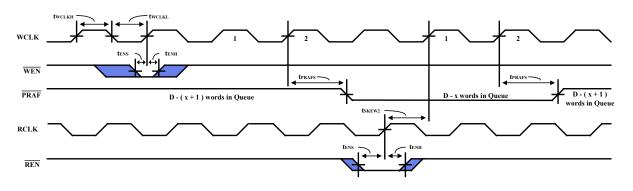

# NOTES:

- 1.  $x = \overline{PRAF}$  offset.

- 2. D = maximum queue depth. Please refer to Table 7 for Depth.

- 3. If the time between a rising edge of RCLK to the rising edge of WCLK is greater than or equal to tskew2, PRAF will go high (after on WCLK cycle plus tPRAFs). If tskew2 is not met, then PRAF will assert 1 or more WCLK cycles.

- 4. **PRAF** synchronizes to the rising edge of WCLK only.

#### Diagram 12. Programmable Almost-Full Flag Timing (Standard and FWFT Mode)

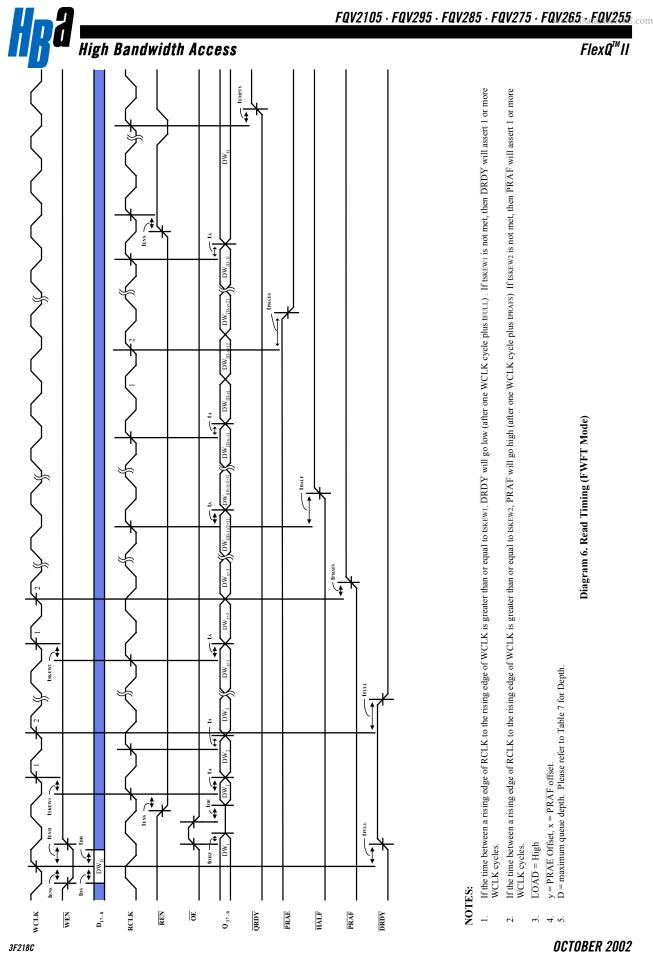

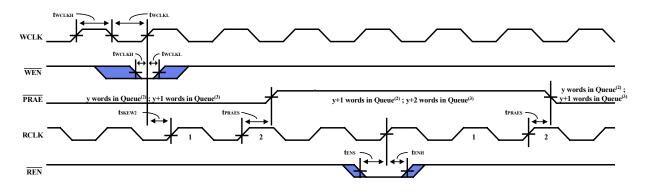

#### NOTES:

- 1.  $y = \overline{PRAE}$  offset.

- 2. For Standard Mode.

- 3. For FWFT Mode.

- 4. If the time between a rising edge of WCLK to the rising edge of RCLK is greater than or equal to tskew2, PRAE will go high (after one RCLK cycle plus tPRAEs). If tskew2 is not met, then PRAE will assert 1 or more RCLK cycles.

- 5. **PRAE** synchronizes to the rising edge of RCLK only.

#### Diagram 13. Programmable Almost-Empty Flag Timing (Standard and FWFT Mode)

#### NOTES:

1. For Standard Mode.

2. For FWFT Mode.

3. Please refer to Table 7 for Depth.